A new application filed with the US Patent and Trademark Office on the last day of last year describes AMD's approach to a potential chiplet-based graphics accelerator design. The manufacturer pointed out the problems in such a design and explained how they could be avoided in the future.

According to AMD, graphics processors are still monolithic chips for a reason: there are plenty of problems with the interaction of multiple chips. The current graphics pipeline is not particularly efficient for multiple GPUs (the same goes for configurations like Crossfire or SLI), as it is sometimes difficult to distribute tasks between multiple active chips in a system. AMD also describes synchronisation of memory content between multiple GPU chips as being complex and costly from a design perspective.

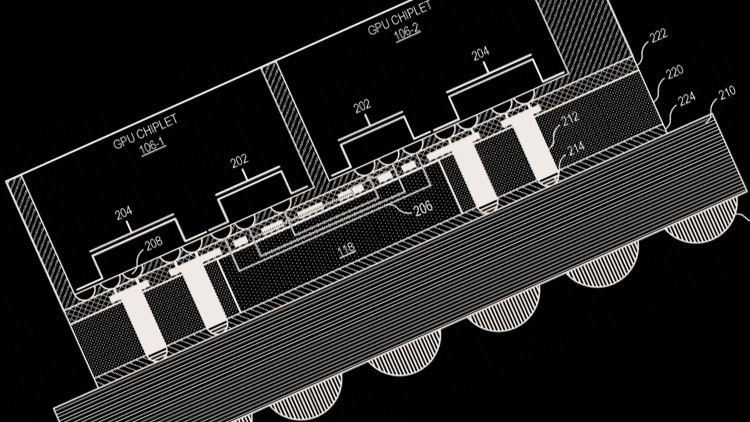

AMD believes that such problems could be avoided by introducing «high bandwidth passive crosslinks». According to AMD, the first GPU chipset should be directly connected to the CPU, while each of the graphics chipsets in the array & ; are connected to the first GPU via passive crosslinks. Such links must be placed in a silicon interposer layer, which is an intermediate wafer with conductors in one or more layers. A group of interconnected chips would work, essentially, like a system on a chip.

Conventional GPUs have a common last-level cache (LLC), but to avoid timing issues AMD believes that each of the chipsets should get their own LLC, with all of them being unified and consistent across all chipsets.

AMD has not publicly confirmed that it is working on a chiplet-based graphics accelerator design. However, there have been rumours that the RDNA 3+ design could be chiplet-based. AMD has a lot of experience with multi-chip designs, especially in its Ryzen processors and various APUs, including gaming consoles.

It is expected that both competitors, NVIDIA and Intel, could also go down this path, allowing them to produce accelerators with higher performance. Intel has already confirmed that it is working on Xe-HP graphics cards with a multi-chip design & ; they are expected to debut this year. NVIDIA is rumoured to unveil its first such accelerator along with the Hopper architecture. Back in 2019, NVIDIA's chief science advisor Bill Dally said that the company has developed technology to build a graphics accelerator with a multi-chip layout.