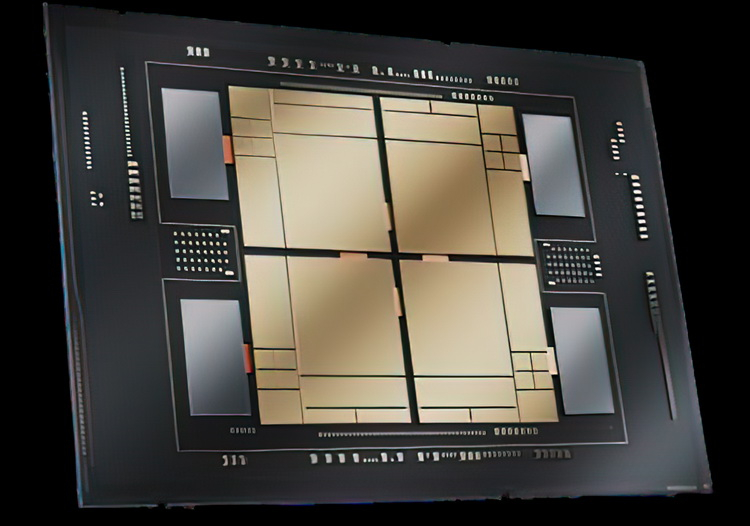

Intel at the International Supercomputing Conference has shared fresh details about its upcoming 4th generation Xeon Scalable server processors, also known as Sapphire Rapids.Processors of this series will be available in two versions: standard and with HBM2e memory.There were fresh details about the latter.Image source: IntelThe standard variant of Sapphire Rapids processors has a chip design of four XCC crystals.The area of each chiplet is about 400 mm2.The crystals will be interconnected by an EMIB bus.These processors will have 10 EMIB interconnects and the total standard Sapphire Rapids-SP processor package area will be 4,446mm2.Sapphire Rapids-SP HBM variants will be able to offer up to 64GB of HBM2e high bandwidth memory in the form of four 16GB stacks each.Given the increased number of chips on the substrate of these processor models including HBM2e memory, these processor versions will have 14 EMIB interconnect points.The total packaging area of Sapphire Rapids-SP HBM will be 28% greater than the standard variant and will be 5,700 mm2. Intel says the EMIB channel will offer twice the bandwidth density and four times the power efficiency compared to standard packaging designs.The company also shared performance data for Sapphire Rapids-SP with HBM2e memory.According to the manufacturer, the next-generation Xeon processors deliver twice the metrology performance of Xeon Ice Lake-SP chips, and they are more than three times faster in the YASK benchmark, have twice the performance in openFOAM (a platform for numerical simulation of continuum mechanics problems), and are more than three times the performance in CloverLeaf. In addition, the company claims that Sapphire Rapids-SP with HBM2e memory will offer twice the performance in fluid dynamics calculations (Ansys Fluent) and twice the performance in ParSeNet. Recall that Sapphire Rapids-SP processors will get up to 56 cores with support for up to 112 virtual threads.They will work with 8-channel DDR5-4800 memory, support up to 80 PCIe 5.0 lanes, and their maximum L3 cache capacity is 105 Mbytes.